INTRO. TO COMP. ENG.

CHAPTER VIII-1

FINITE STATE MACHINES

•CHAPTER VIII

# CHAPTER VIII FINITE STATE MACHINES (FSM)

# STATE MACHINES

# •STATE MACHINES -INTRODUCTION

#### **FINITE STATE MACHINES**

INTRODUCTION

- From the previous chapter we can make simple memory elements.

- Latches as well as latches with control signals

- Flip-flops

- Registers

- The goal now is to use the memory elements to hold the running state of the machine.

- The state of the machine can be used to perform sequential operations.

- This chapter will discuss how to represent the state of the machine for design and communication purposes.

#### **FINITE STATE MACHINES**

### **STATE MACHINES**

**MEALY & MOORE MACHINES**

•STATE MACHINES

-INTRODUCTION

### Mealy machine

Sequential system where output depends on current input and state.

#### Moore machine

Sequential system where output depends only on current state.

#### **FINITE STATE MACHINES**

### STATE MACHINES

SYNC. & ASYNC. SYSTEMS

•STATE MACHINES

-INTRODUCTION

-MEALY & MOORE MACH.

### Synchronous sequential system

- Behaviour depends on the inputs and outputs at discrete instants of time.

- Flip-flops, registers, and latches that are enabled/controlled with a signal derived from clock form a synchronous sequential system.

- Asynchronous sequential system

- Behaviour depends on inputs at any instant of time.

- Latches without control signals behave in an asynchronous manner.

- The state machines discussed in this chapter will be synchronous sequential systems (i.e. controlled by a clock)

- This allows us to form timed Boolean functions such as

- $N(t) = D_A(t+1)$  where N is the next state of a D flip-flop  $D_A$ .

#### **FINITE STATE MACHINES**

### **STATE DIAGRAMS**

**ELEMENTS OF DIAGRAMS**

- STATE MACHINES

- -INTRODUCTION

- -MEALY & MOORE MACH.

- -SYNC. & ASYNC SYSTEMS

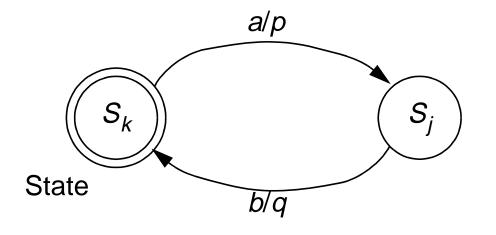

- A state diagram represents a finite state machine (FSM) and contains

- Circles: represent the machine states

- Labelled with a binary encoded number or  $S_k$  reflecting state.

- **Directed arcs**: represent the transitions between states

- Labelled with input/output for that state transition.

Input:

$x(t) \in \{a, b\}$

Output:

$z(t) \in \{p, q\}$

State:

$s(t) \in \{S_k, S_j\}$

Initial state:

$s(0) = S_k$

Input/Output

FINITE STATE MACHINES

### STATE DIAGRAMS

#### **PROPERTIES**

•STATE MACHINES

•STATE DIAGRAMS

-ELEMENTS OF DIAGRAMS

- Some restrictions that are placed on the state diagrams:

- FSM can only be in one state at a time!

- Therefore, only in one state, or one circle, at a time.

- State transitions are followed only on clock cycles. (synchronous!)

- Mealy machines and Moore machines can be labelled differently.

- Mealy machine: Since output depends on state and inputs:

- Label directed arcs with input/output for that state transition.

- Moore machine: Since output depends only on state:

- Label directed arcs with input for that state transistion.

- Label state circles with  $S_k$ /output.

#### **FINITE STATE MACHINES**

### **STATE DIAGRAMS**

STATE DIAGRAM EXAMPLES

- •STATE MACHINES

•STATE DIAGRAMS

-ELEMENTS OF DIAGRAMS

-PROPERTIES

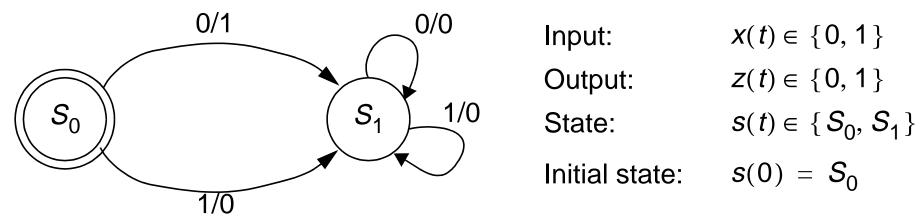

- The following is a simple example. What does this state machine do?

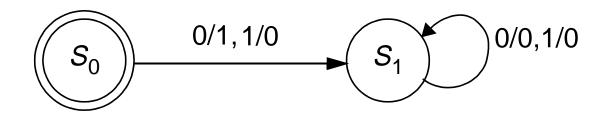

Here is a simplified way of forming the above state machine.

• An input of 0 or 1 causes the transition with output 1 and 0, respectively.

#### **FINITE STATE MACHINES**

### STATE DIAGRAMS

#### BIT FLIPPER EXAMPLE

•STATE DIAGRAMS

- -ELEMENTS OF DIAGRAMS

- -PROPERTIES

- -STATE DIAGRAM EX.

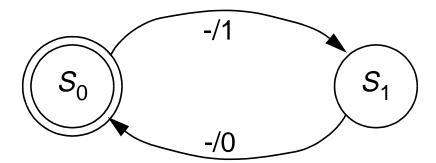

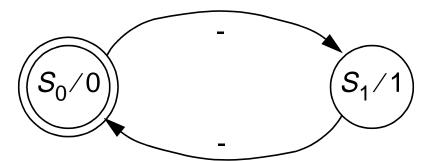

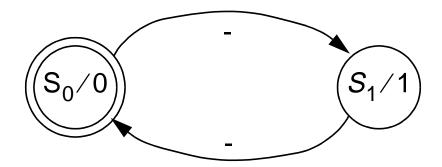

- Consider the simple bit flipper looked at the in previous chapter. How would a state diagram be formed?

- Below is one possible way of drawing the state diagram for the bit flipper.

• Since the bit flipper is a Moore machine, the state diagram can also be

#### **FINITE STATE MACHINES**

### **STATE DIAGRAMS**

PATTERN DETECT EXAMPLE

•STATE DIAGRAMS

- -PROPERTIES

- -STATE DIAGRAM EX.

- -BIT FLIPPER EX.

- Suppose we want a sequential system that has the following behaviour

Input:

$$x(t) \in \{0, 1\}$$

Output:

$$z(t) \in \{0, 1\}$$

Function:

$$z(t) = \begin{cases} \mathbf{1} & \text{if } x(t-3, t) = \mathbf{1101} \\ \mathbf{0} & \text{otherwise} \end{cases}$$

- Effectively, the system should output a 1 when the last set of four inputs have been 1101.

- For instance, the following output z(t) is obtained for the input x(t)

| t    | 0123456789                                                |

|------|-----------------------------------------------------------|

| X(t) | 100100100100 <b>1101</b> 0 <b>1101</b> 00 <b>1101</b> 001 |

| Z(t) | ???00000000000100001001000001000                          |

#### **FINITE STATE MACHINES**

### STATE DIAGRAMS

#### PATTERN DETECT EXAMPLE

- •STATE DIAGRAMS

- -STATE DIAGRAM EX.

- -BIT FLIPPER EX.

- -PATTERN DETECT EX.

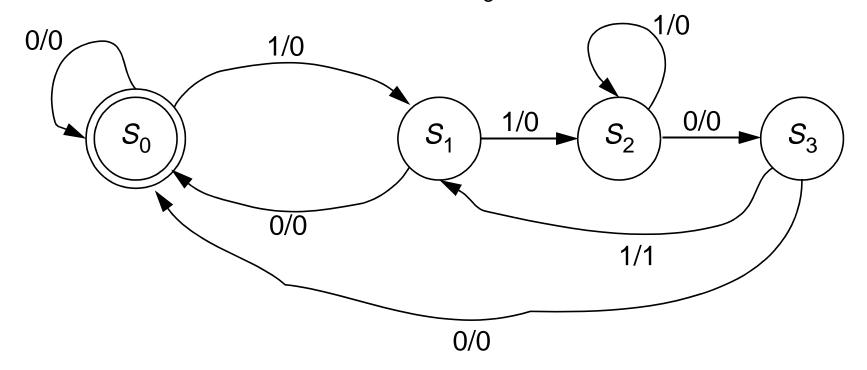

- The following state diagram gives the behaviour of the desired 1101 pattern detector.

- Consider  $S_0$  to be the initial state,  $S_1$  when first symbol detected (1),  $S_2$  when subpattern 11 detected, and  $S_3$  when subpattern 110 detected.

### **FINITE STATE MACHINES**

### STATE TABLES

#### INTRODUCTION

•STATE DIAGRAMS

- -STATE DIAGRAM EX.

- -BIT FLIPPER EX.

- -PATTERN DETECT EX.

- State tables also express a systems behaviour and consists of

- Present state

- The present state of the system, typically given in binary encoded form or with S<sub>k</sub>. So, a state of S<sub>5</sub> in our state diagram with 10 states would be represented as 0101 since we require 4 bits.

- Inputs

- Whatever external inputs used to cause the state transitions.

- Next state

- The next state, generally in binary encoded form.

- Outputs

- Whatever outputs, other then the state, for the system. Note that there would be no outputs in a Moore machine.

#### **FINITE STATE MACHINES**

# **STATE TABLES**

#### BIT FLIPPER EXAMPLE

•STATE DIAGRAMS

•STATE TABLES

-INTRODUCTION

Consider again the bit flipper example with state diagram

The state table for this state diagram would be

| Present State                     | Input | Next State | Output |

|-----------------------------------|-------|------------|--------|

| $\mathcal{S}_0$ or $oldsymbol{0}$ | -     | 1          | -      |

| S₁ or <b>1</b>                    | -     | 0          | -      |

#### **FINITE STATE MACHINES**

### STATE TABLES

#### TRANSLATE FROM DIAGRAM

•STATE DIAGRAMS

•STATE TABLES

-INTRODUCTION

-BIT FLIPPER EX.

- From a state diagram, a state table is fairly easy to obtain.

- Determine the number of states in the state diagram.

- If there are *m* states and *n* 1-bit inputs, then there will be  $m2^n$  rows in the state table.

- Example: If there are 3 states and 2 1-bit inputs, each state will have 2<sup>2</sup> = 4 possible inputs, for a total of 3\*4=12 rows.

- Write out for each state, the 2<sup>n</sup> possible input rows.

- For each state/input pair, follow the directed arc in the state diagram to determine the next state and the output.

#### **FINITE STATE MACHINES**

### STATE TABLES

#### PATTERN DETECT EXAMPLE

•STATE TABLES

-INTRODUCTION

-BIT FLIPPER EX.

-TRANSLATE DIAGRAM

• If we consider the pattern detection example previously discussed, the following would be the state table.

| Present State |                |                | Input | Next State |                | Output         |   |

|---------------|----------------|----------------|-------|------------|----------------|----------------|---|

|               | P <sub>1</sub> | P <sub>0</sub> | X     |            | N <sub>1</sub> | N <sub>0</sub> | Z |

| $S_0$ or      | 0              | 0              | 0     | $S_0$ or   | 0              | 0              | 0 |

| $S_0$ or      | 0              | 0              | 1     | $S_1$ or   | 0              | 1              | 0 |

| $S_1$ or      | 0              | 1              | 0     | $S_0$ or   | 0              | 0              | 0 |

| $S_1$ or      | 0              | 1              | 1     | $S_2$ or   | 1              | 0              | 0 |

| $S_2$ or      | 1              | 0              | 0     | $S_3$ or   | 1              | 1              | 0 |

| $S_2$ or      | 1              | 0              | 1     | $S_2$ or   | 1              | 0              | 0 |

| $S_3$ or      | 1              | 1              | 0     | $S_0$ or   | 0              | 0              | 0 |

| $S_3$ or      | 1              | 1              | 1     | $S_1$ or   | 0              | 1              | 1 |

#### **FINITE STATE MACHINES**

### STATE TABLES

#### TRANSLATE TO DIAGRAM

•STATE TABLES

-BIT FLIPPER EX.

-TRANSLATE DIAGRAM

-PATTERN DETECT EX.

- If given a state table, the state diagram can be developed as follows.

- Determine the number of states in the table and draw a state circle corresponding to each one.

- Label the circle with the state name for a Mealy machine.

- Label the circle with the state name/output for a Moore machine.

- For each row in the table, identify the present state circle and draw a directed arc to the next state circle.

- Label the arc with the input/output pair for a Mealy machine.

- Label the arc with the input for a Moore machine.

#### **FINITE STATE MACHINES**

### **SEQ. CIRCUITS**

#### INTRODUCTION

STATE TABLES

- -TRANSLATE DIAGRAM

- -PATTERN DETECT EX.

- -TRANSLATE TO DIAGRAM

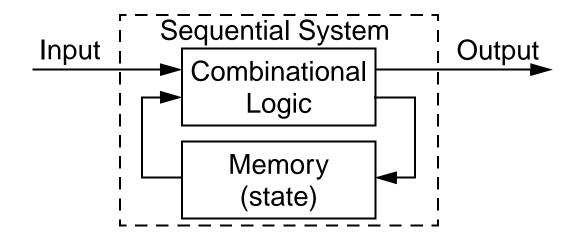

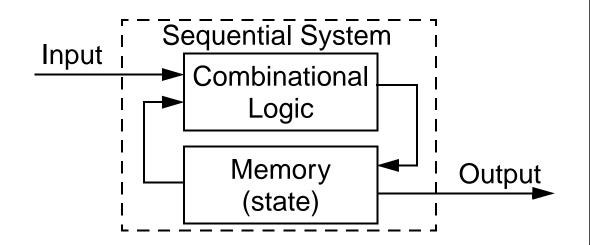

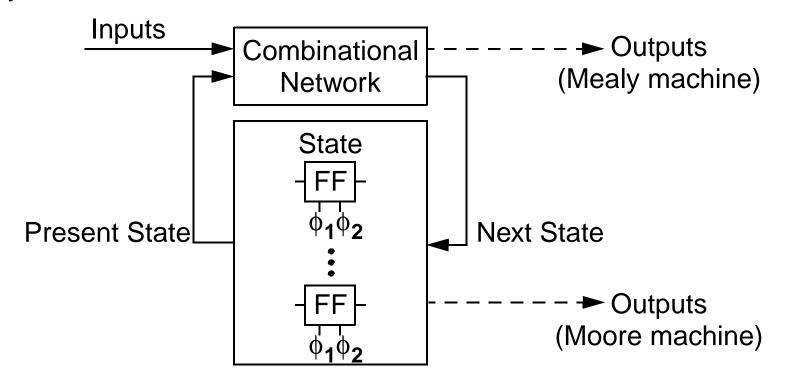

- With the descriptions of a FSM as a state diagram and a state table, the next question is how to develop a sequential circuit, or logic diagram from the FSM.

- Effectively, we wish to form a circuit as follows.

#### **FINITE STATE MACHINES**

### **SEQ. CIRCUITS**

#### FROM STATE TABLE

•STATE TABLES

•SEQUENTIAL CIRCUITS

-INTRODUCTION

- The procedure for developing a logic circuit from a state table is the same as with a regular truth table.

- Generate Boolean functions for

- each external outputs using external inputs and present state bits

- each next state bit using external inputs and present state bits

- Use Boolean algebra, Karnaugh maps, etc. as normal to simplify.

- Draw a register for each state bit.

- Draw logic diagram components connecting external outputs to external inputs and outputs of state bit registers (which have the present state).

- Draw logic diagram components connecting inputs of state bits (for next state) to the external inputs and outputs of state bit registers (which have the present state).

#### **FINITE STATE MACHINES**

### **SEQ. CIRCUITS**

#### PATTERN DETECT EXAMPLE

•STATE TABLES

•SEQUENTIAL CIRCUITS

-INTRODUCTION

-DEVEL. LOGIC CIRCUITS

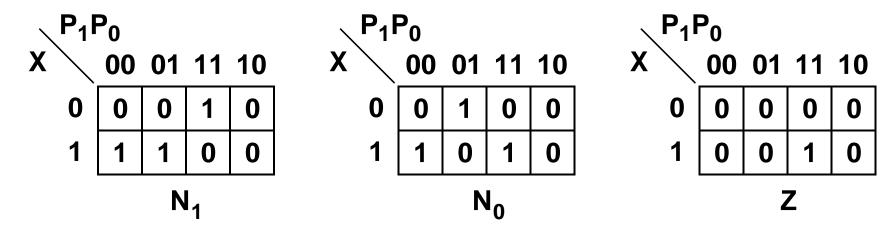

Following the procedure outlined, Boolean functions for the pattern detector state table can be formed using Karnaugh maps as follows.

$$\begin{split} &N_1 = X\overline{P_1} + \overline{X}P_1P_0 \\ &N_0 = \overline{X}\overline{P_1}P_0 + XP_1P_0 + X\overline{P_1}\overline{P_0} = \overline{X}\overline{P_1}P_0 + X(\overline{P_1 \oplus P_0}) \\ &Z = XP_1P_0 \end{split}$$

#### **FINITE STATE MACHINES**

### **SEQ. CIRCUITS**

#### PATTERN DETECT EXAMPLE

- •SEQUENTIAL CIRCUITS

- -INTRODUCTION

- -DEVEL. LOGIC CIRCUITS

- -PATTERN DETECT EX.

- Notice that the previous Boolean functions can also be expressed with time as follows.

$$\begin{split} \mathbf{N_1}(t) &= \mathbf{P_1}(t+1) = \mathbf{X}(t) \cdot \overline{\mathbf{P_1}(t)} + \overline{\mathbf{X}(t)} \cdot \mathbf{P_1}(t) \cdot \mathbf{P_0}(t) \\ \mathbf{N_0}(t) &= \mathbf{P_0}(t+1) = \overline{\mathbf{X}(t)} \cdot \overline{\mathbf{P_1}(t)} \cdot \mathbf{P_0}(t) + \mathbf{X}(t) \cdot \overline{\mathbf{P_1}(t)} \cdot \overline{\mathbf{P_0}(t)} \\ &+ \mathbf{X}(t) \cdot \overline{\mathbf{P_1}(t)} \cdot \overline{\mathbf{P_0}(t)} \\ &= \overline{\mathbf{X}(t)} \cdot \overline{\mathbf{P_1}(t)} \cdot \mathbf{P_0}(t) + \mathbf{X}(t) \cdot \overline{\mathbf{P_1}(t)} \oplus \overline{\mathbf{P_0}(t)} \\ \mathbf{Z}(t) &= \mathbf{X} \cdot \mathbf{P_1}(t) \cdot \mathbf{P_0}(t) \end{split}$$

An important thing to note in these equations is the relation between the present states P and the next states N.

#### **FINITE STATE MACHINES**

### **SEQ. CIRCUITS**

#### PATTERN DETECT EXAMPLE

- •SEQUENTIAL CIRCUITS

- -INTRODUCTION

- -DEVEL. LOGIC CIRCUITS

- -PATTERN DETECT EX.

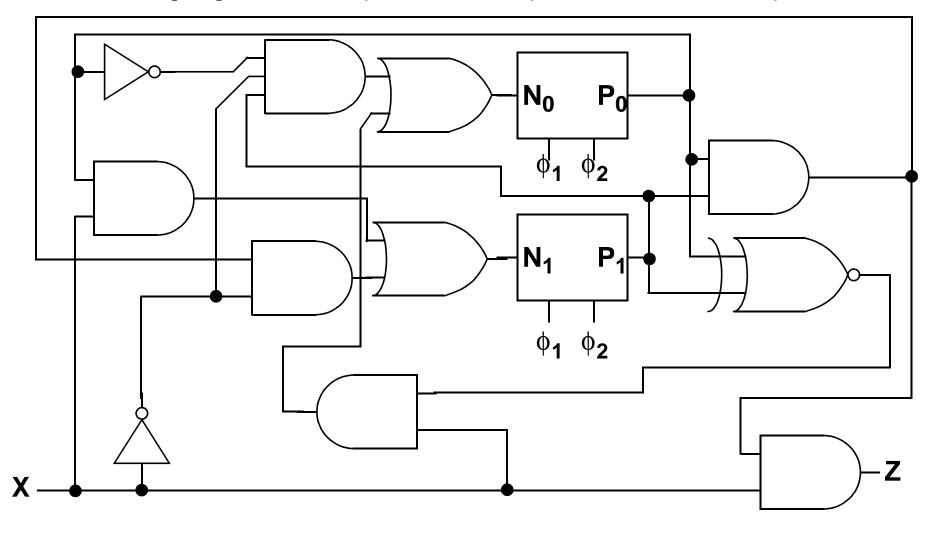

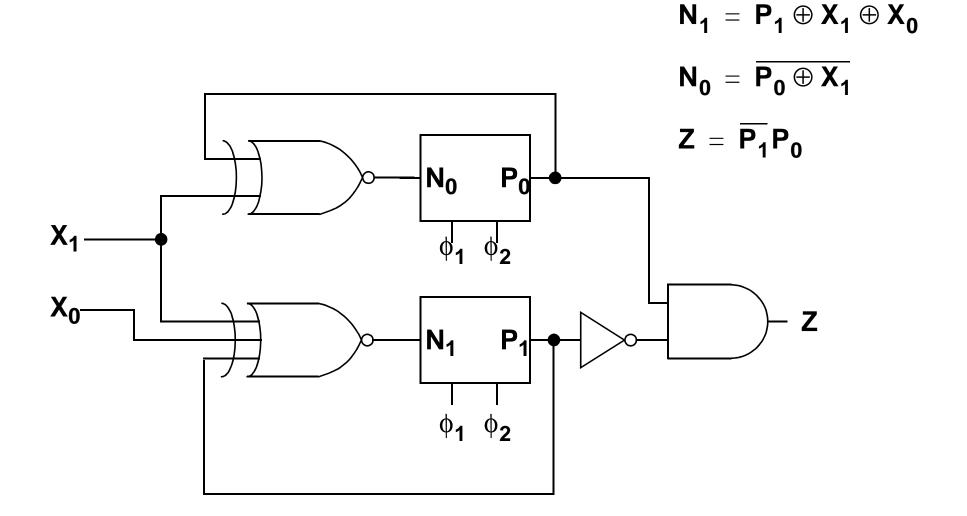

- The following logic circuit implements the pattern detect example.

FINITE STATE MACHINES

### **FSM EXAMPLES**

#### EXAMPLE #1

•SEQUENTIAL CIRCUITS

- -INTRODUCTION

- -DEVEL. LOGIC CIRCUITS

- -PATTERN DETECT EX.

- · Consider the following system description.

- A sequential system has

- One input = {**a**, **b**, **c**}

- One output = {**p**, **q**}

- Output is

- q when input sequence has even # of a's and odd # of b's

- **p** otherwise

**FINITE STATE MACHINES**

### **FSM EXAMPLES**

#### EXAMPLE #1

•SEQUENTIAL CIRCUITS

•FSM EXAMPLES

-EXAMPLE #1

- We can begin forming a state machine for the system description by reviewing the possible states. In addition, assign each state a state name.

- S<sub>FF</sub>: even # of a's and even # of b's / output is p

- S<sub>EO</sub>: even # of a's and odd # of b's / output is q

- $S_{OO}$ : odd # of **a**'s and odd # of **b**'s / output is **p**

- S<sub>OF</sub>: odd # of a's and even # of b's / output is p

- Note that this machine can be a Moore machine. So, we can associate the output with each state.

FINITE STATE MACHINES

### **FSM EXAMPLES**

EXAMPLE #1

•SEQUENTIAL CIRCUITS

•FSM EXAMPLES

-EXAMPLE #1

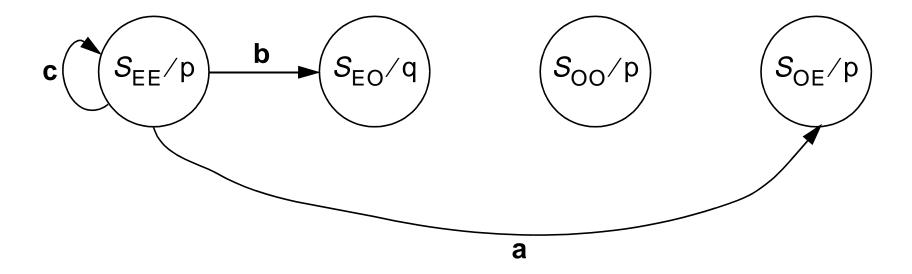

Now draw a circle with each state.

### **FSM EXAMPLES**

EXAMPLE #1

•SEQUENTIAL CIRCUITS

•FSM EXAMPLES

-EXAMPLE #1

- FINITE STATE MACHINES

- Finally, for each state, consider the effect for each possible input.

- For instance, starting with state S<sub>EE</sub>, the next state for the three input a,

b, and c are determined as follows.

### **FSM EXAMPLES**

EXAMPLE #1

•SEQUENTIAL CIRCUITS

•FSM EXAMPLES

-EXAMPLE #1

FINITE STATE MACHINES

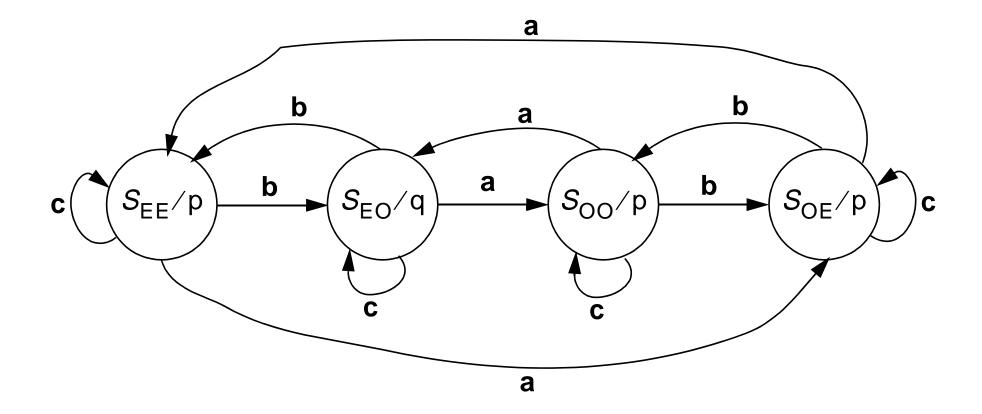

• Finishing the state diagram, the following is obtained.

### **FSM EXAMPLES**

#### **FINITE STATE MACHINES**

EXAMPLE #1

•SEQUENTIAL CIRCUITS

•FSM EXAMPLES

-EXAMPLE #1

- A state table can also be formed for this state diagram as follows.

- First, assign a binary number to each state

•

$$S_{EE} = 00$$

,  $S_{EO} = 01$ ,  $S_{OO} = 10$ ,  $S_{OE} = 11$

- Assign a binary number to each input

- a = 00, b = 01, c = 10

- Assign a binary number to each output

- p = 0, q = 1

- Then for each state, find the next state for each input. In this case there

are three possible input values, so, three possible state transitions from

each state.

- The state table on the following slide shows the results for this example.

FINITE STATE MACHINES

### **FSM EXAMPLES**

EXAMPLE #1

•SEQUENTIAL CIRCUITS

•FSM EXAMPLES

-EXAMPLE #1

| Present State  |                | Input  | Next State          |                | Output       |

|----------------|----------------|--------|---------------------|----------------|--------------|

| P <sub>1</sub> | P <sub>0</sub> | X      | N <sub>1</sub>      | N <sub>0</sub> | Z            |

| $S_{EE} = 0$   | 0              | a = 00 | S <sub>OE</sub> = 1 | 1              | p = 0        |

| $S_{EE} = 0$   | 0              | b = 01 | $S_{EO} = 0$        | 1              | p = 0        |

| $S_{EE} = 0$   | 0              | c = 10 | $S_{EE} = 0$        | 0              | p = 0        |

| $S_{EO} = 0$   | 1              | a = 00 | $S_{OO} = 1$        | 0              | <b>q</b> = 1 |

| $S_{EO} = 0$   | 1              | b = 01 | $S_{EE} = 0$        | 0              | <b>q</b> = 1 |

| $S_{EO} = 0$   | 1              | c = 10 | $S_{EO} = 0$        | 1              | <b>q</b> = 1 |

| $S_{OO} = 1$   | 0              | a = 00 | $S_{EO} = 0$        | 1              | p = 0        |

| $S_{OO} = 1$   | 0              | b = 01 | $S_{OE} = 1$        | 1              | p = 0        |

| $S_{OO} = 1$   | 0              | c = 10 | $S_{OO} = 1$        | 0              | p = 0        |

| $S_{OE} = 1$   | 1              | a = 00 | $S_{EE} = 0$        | 0              | p = 0        |

| $S_{OE} = 1$   | 1              | b = 01 | $S_{OO} = 1$        | 0              | p = 0        |

| $S_{OE} = 1$   | 1              | c = 10 | $S_{OE} = 1$        | 1              | p = 0        |

### **FSM EXAMPLES**

EXAMPLE #1

•SEQUENTIAL CIRCUITS

•FSM EXAMPLES

-EXAMPLE #1

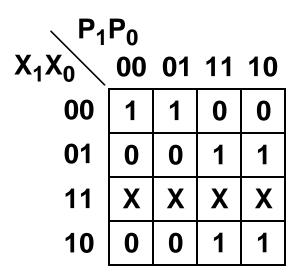

**FINITE STATE MACHINES**

- The Boolean function for the output can be determined from a Karnaugh map as follows.

- Note that an input of **11** is not possible since we only have three inputs that we have assigned to **00**, **01**, and **10**. We can therefore use don't cares for this possible input.

$$Z = \overline{P_1}P_0$$

### **FSM EXAMPLES**

**FINITE STATE MACHINES**

EXAMPLE #1

•SEQUENTIAL CIRCUITS

•FSM EXAMPLES

-EXAMPLE #1

The Boolean function for the next state bit can also be determined from Karnaugh maps as follows.

$$N_1 = \overline{P_1 \oplus X_1 \oplus X_0}$$

$$N_0 = P_0 X_1 + \overline{P_0} \overline{X_1} = \overline{P_0 \oplus X_1}$$

### **FSM EXAMPLES**

EXAMPLE #1

•SEQUENTIAL CIRCUITS

•FSM EXAMPLES

-EXAMPLE #1

FINITE STATE MACHINES

The following logic circuit can be made with these Boolean functions.

### **FSM EXAMPLES**

#### **FINITE STATE MACHINES**

EXAMPLE #2

•SEQUENTIAL CIRCUITS

•FSM EXAMPLES

-EXAMPLE #1

- A sequential circuit is defined by the following Boolean functions with input

X, present states P<sub>0</sub>, P<sub>1</sub>, and P<sub>2</sub>, and next states N<sub>0</sub>, N<sub>1</sub>, and N<sub>2</sub>.

- $N_2 = X(P_1 \oplus P_0) + \overline{X}(\overline{P_1 \oplus P_0})$

- $\bullet \ \ N_1 = P_2$

- $N_0 = P_1$

- $Z = XP_1P_2$

- Derive the state table.

- Derive the state diagram.

# **FSM EXAMPLES**

EXAMPLE #2

•SEQUENTIAL CIRCUITS

- •FSM EXAMPLES

- -EXAMPLE #1

- -EXAMPLE #2

FINITE STATE MACHINES

The state table is formed as follows.

| Present State                            | Input  | Next State                                               | Output |

|------------------------------------------|--------|----------------------------------------------------------|--------|

| $P_2$ $P_1$ $P_0$                        | X      | $N_2$ $N_1$ $N_0$                                        | Z      |

| 0 0 0                                    | 0      | 1 0 0                                                    | 0      |

| $\begin{matrix}0&0&0\\0&0&1\end{matrix}$ | Ó      | $\begin{array}{cccc} 0 & 0 & 0 \\ 0 & 0 & 0 \end{array}$ | 0      |

| 0 0 1                                    | 1      | 1 0 0                                                    | 0      |

| 0 1 0                                    | U<br>1 | 0 0 1                                                    | 0      |

| 0 1 1                                    | Ó      | 1 0 1                                                    | Ŏ      |

| 0 1 1                                    | 1      | 0 0 1                                                    | 0      |

| 1 0 0<br>1 0 0                           | 0<br>1 | 1 1 0                                                    | 0      |

| 1 0 0                                    | Ó      | 0 1 0                                                    | 0      |

| 1 0 1                                    | 1      | 1 1 0                                                    | 0      |

| 1 1 0                                    | 0      | 0 1 1                                                    | 0      |

| 1 1 0                                    | Ó      | 1 1 1<br>1 1 1                                           | 0      |

| <b>i i i</b>                             | 1      | <b>0</b> 1 1                                             | Ĭ      |

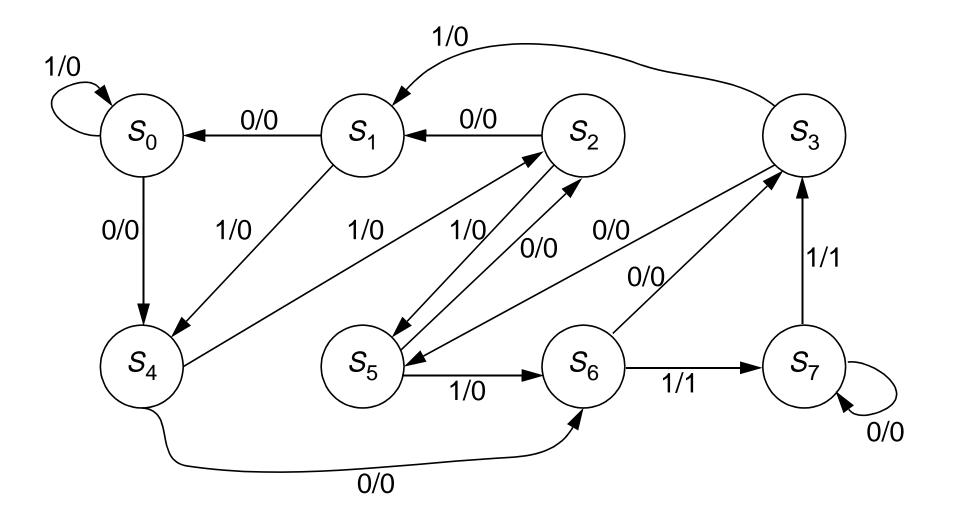

#### **FINITE STATE MACHINES**

### **FSM EXAMPLES**

EXAMPLE #2

•SEQUENTIAL CIRCUITS

- •FSM EXAMPLES

- -EXAMPLE #1

- -EXAMPLE #2

The state diagram can be drawn as follows.