### ECE 6133 Physical Design Automation of VLSI Systems Spring 2013

### Polish Expression Based Floorplanning

Jatin Modi Kshitiz Gupta

### **Project Overview**

- What is the project about?

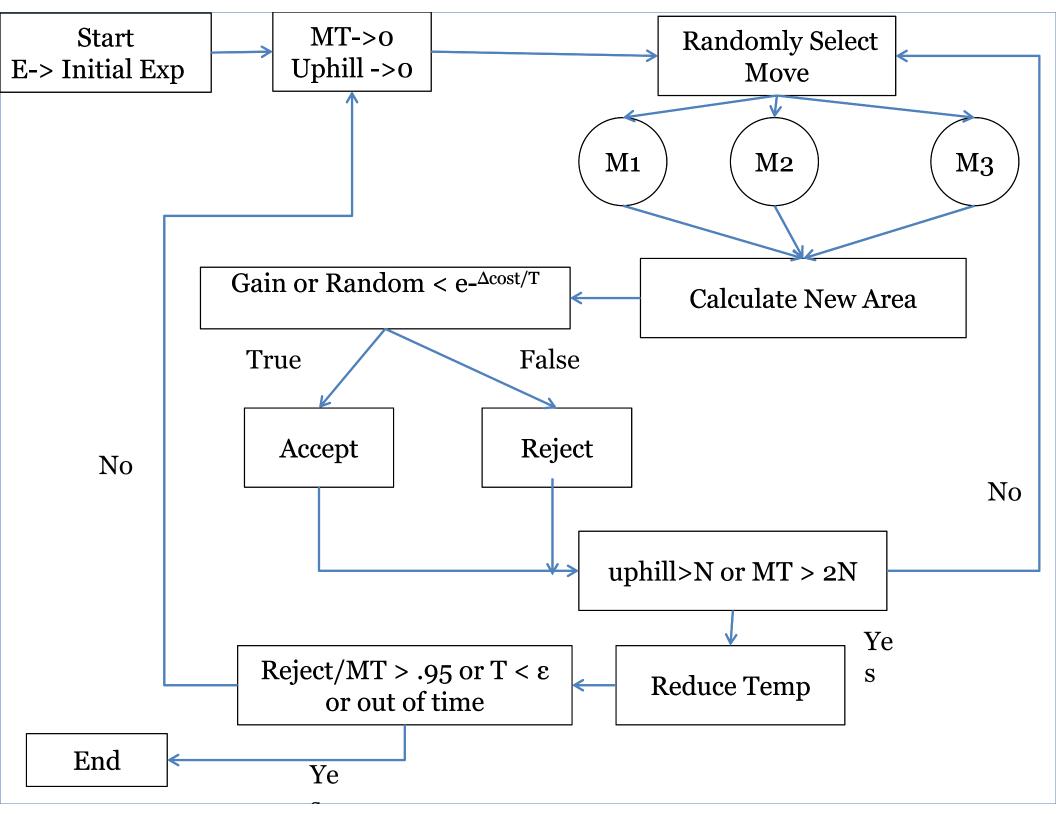

- Using Normalized polish expression based Simulated annealing to determine the location of block in a floorplan.

- Goal of the project ?

- Generate floorplan without overlaps and reduce the total floorplan area.

- Scope?

- $_{\circ}~$  Used rectangular shaped hard blocks with no rotation allowed.

- Language used ?

- $\circ$  C++ and Java

### Normalized Polish Expression

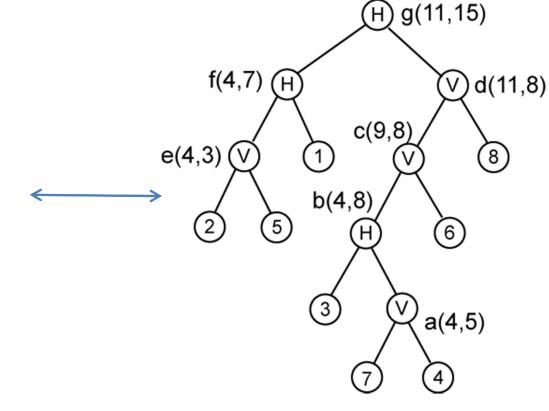

- Polish expression can be obtained from the post- order traversal on binary tree.

- A polish expression which does not have any consecutive operators of same type (H or V).

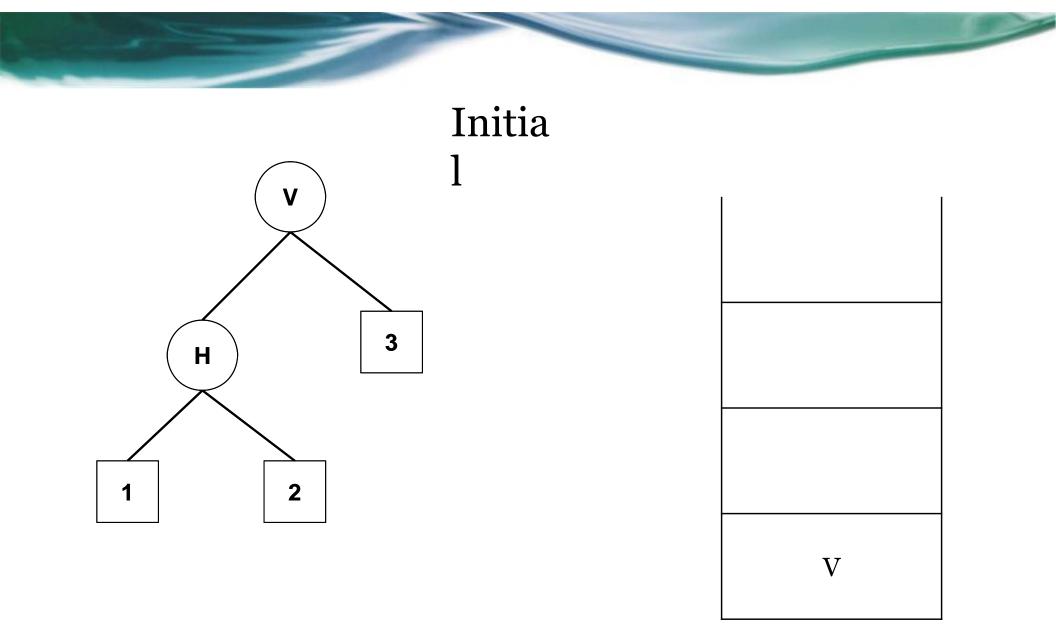

- Using LIFO structure to convert polish expression to binary tree.

PE = 25V1H374VH6V8VH

# Algorithm

### Data Structures

- Arrays

- For storing width and height of each block.

- For storing the polish expression.

- Stacks

- For calculating area and generating trees.

- Binary Trees

- For calculating the coordinates and generating graphs.

### Implementation

- Parse the initial normalized polish expression and the size of the blocks from a text file.

- Store the polish expression as integer array where H and V are replaced by -1 and -2 respectively.

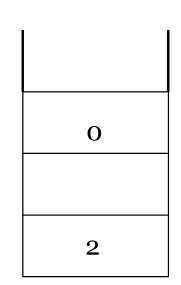

- Cost function was defined as the total Area of floorplan which is calculated as following : 2 1 0 H V

| Block<br>No | Size |

|-------------|------|

| 0           | 1,3  |

| 1           | 5,1  |

| 2           | 3,3  |

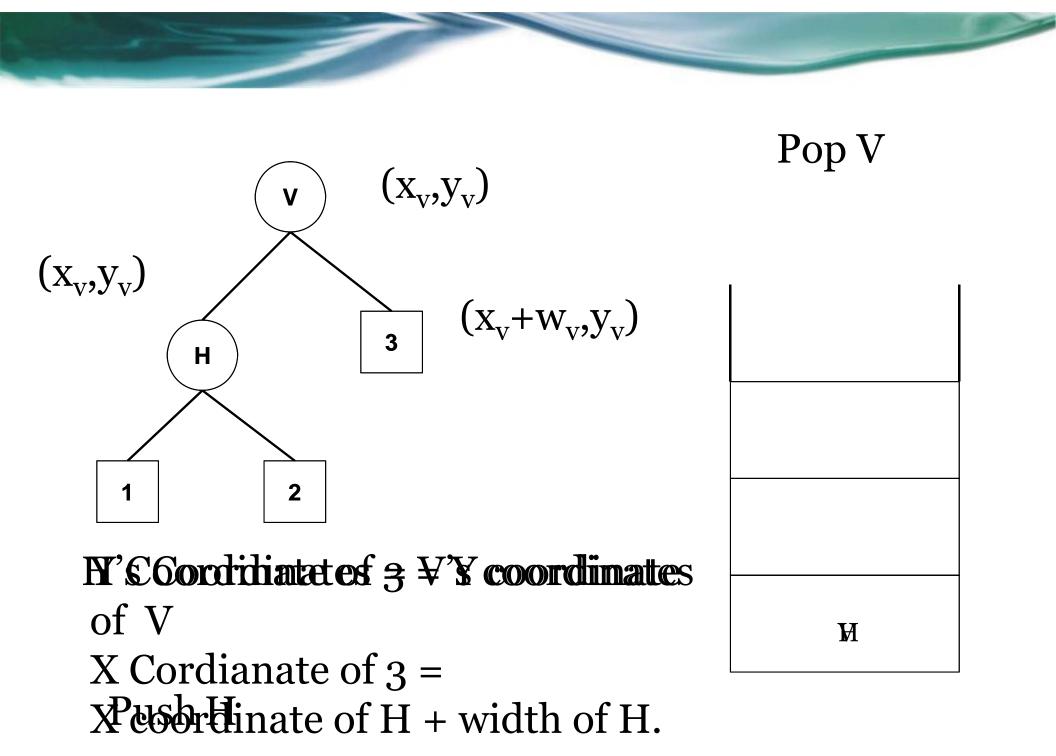

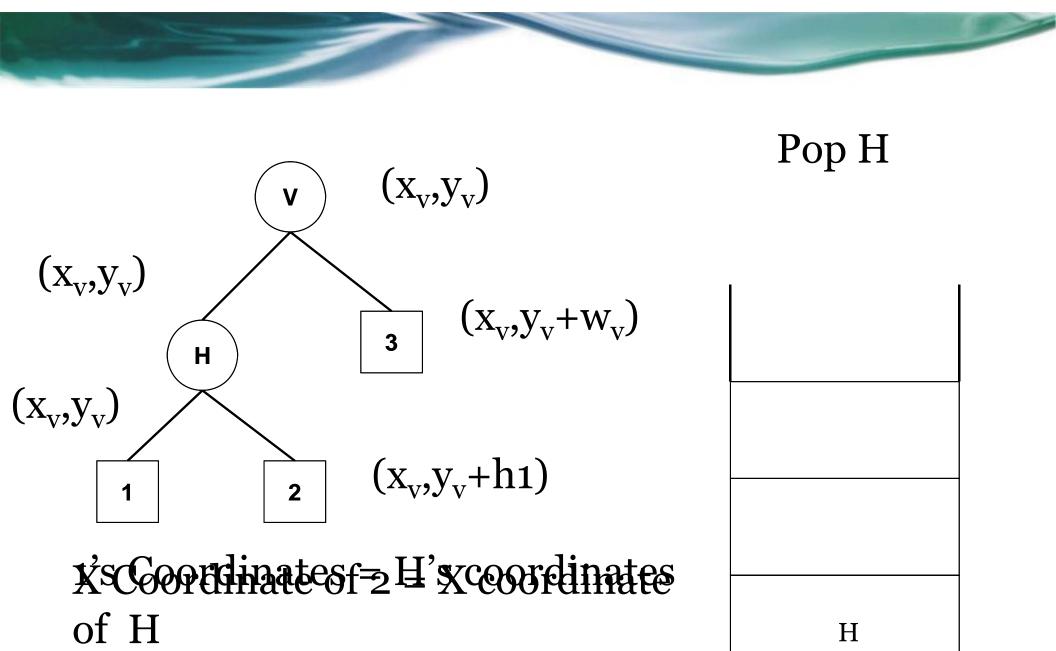

### Calculating the floorplan coordinates

• Block Orientation :-

- First we create a binary tree from the polish expression by using a stack.

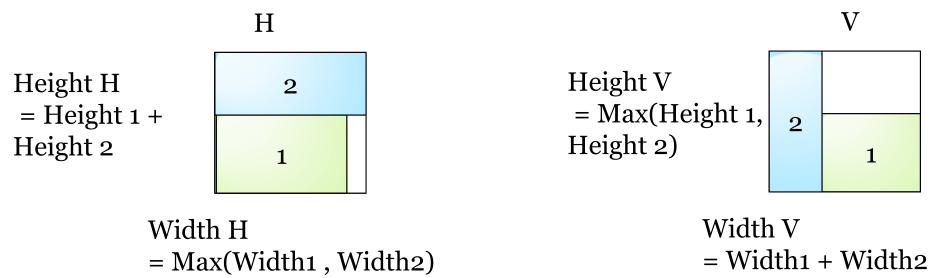

- While creating tree we also calculate the size of each room which is as following :-

### Push V in stack

- Y Cordianate of 2 =

- Y coordinate of H + height of H.

## Demo

### Parameters Used

| No. of<br>Block | Initial Temp | k  | Cooling<br>Ratio | Freezing<br>Temp |

|-----------------|--------------|----|------------------|------------------|

| 5               | 200          | 16 | 0.96             | 144.277          |

| 10              | 320          | 16 | 0.96             | 2.38613          |

| 30              | 380          | 15 | 0.96             | 2.7201           |

| 100             | 3422         | 16 | 0.96             | 0.00393676       |

| 150             | 10040        | 20 | 0.99             | 0.000032         |

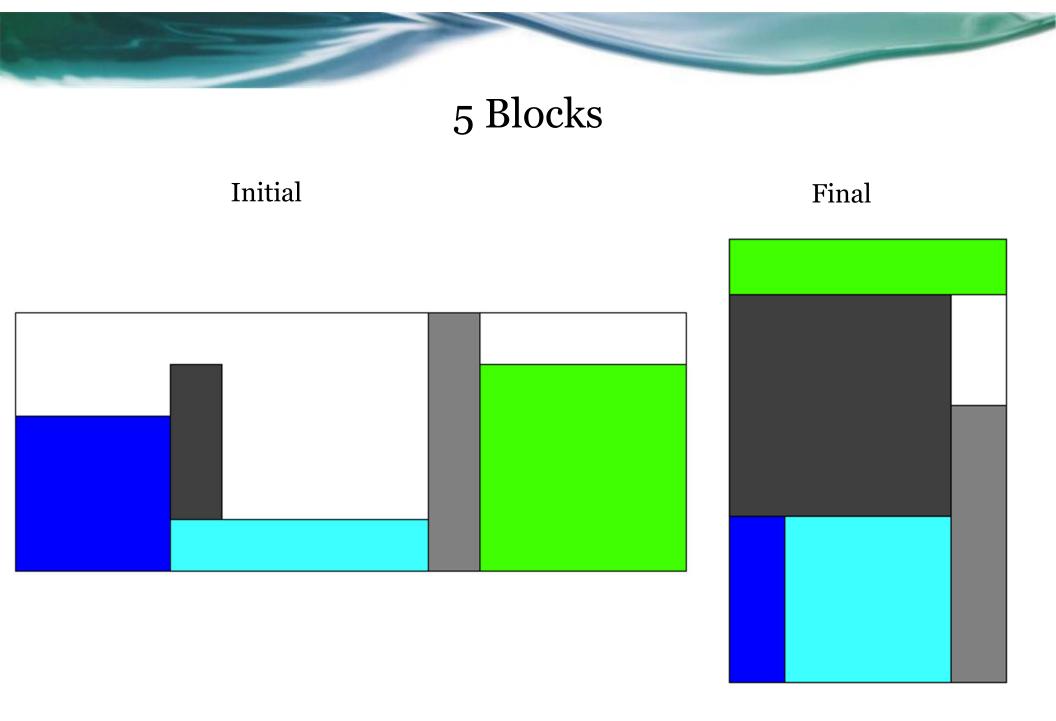

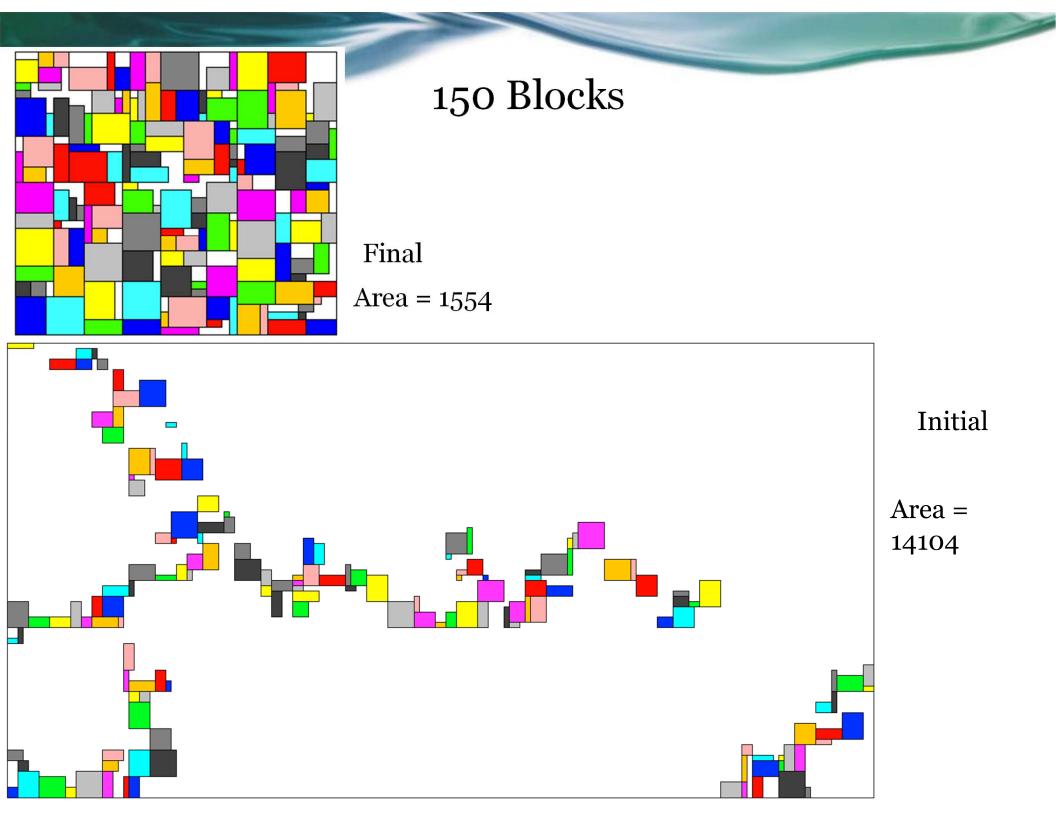

# Floorplans

Area = 40

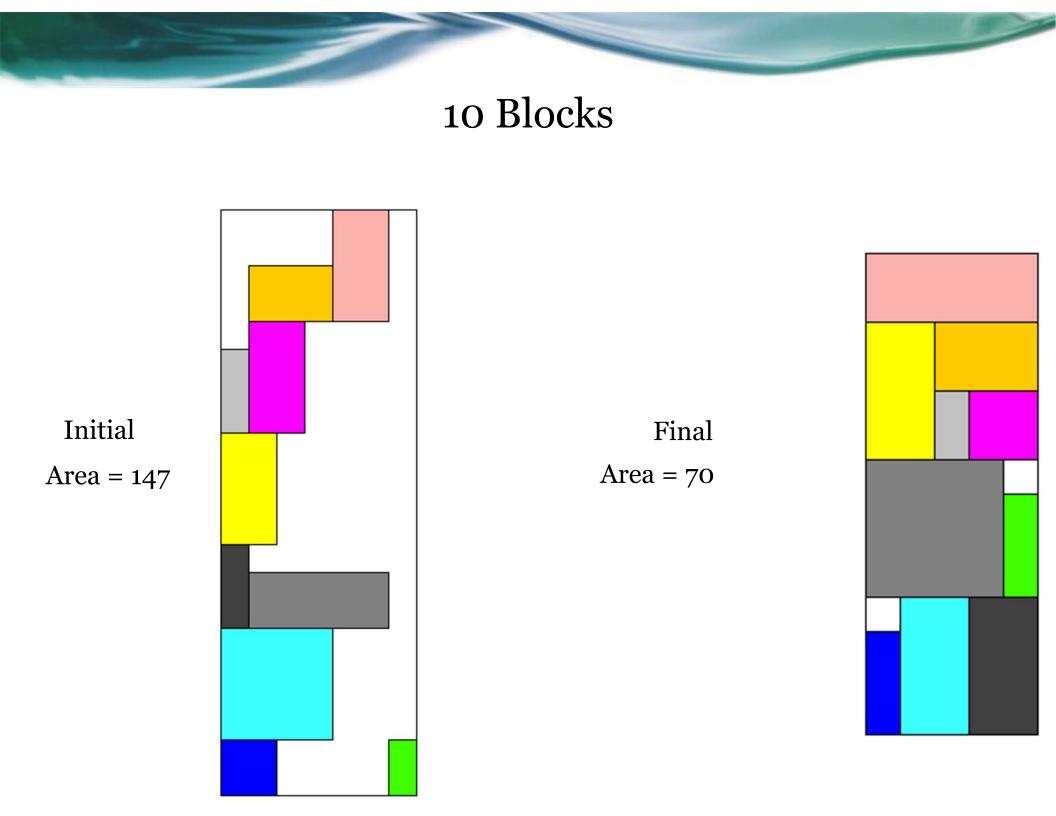

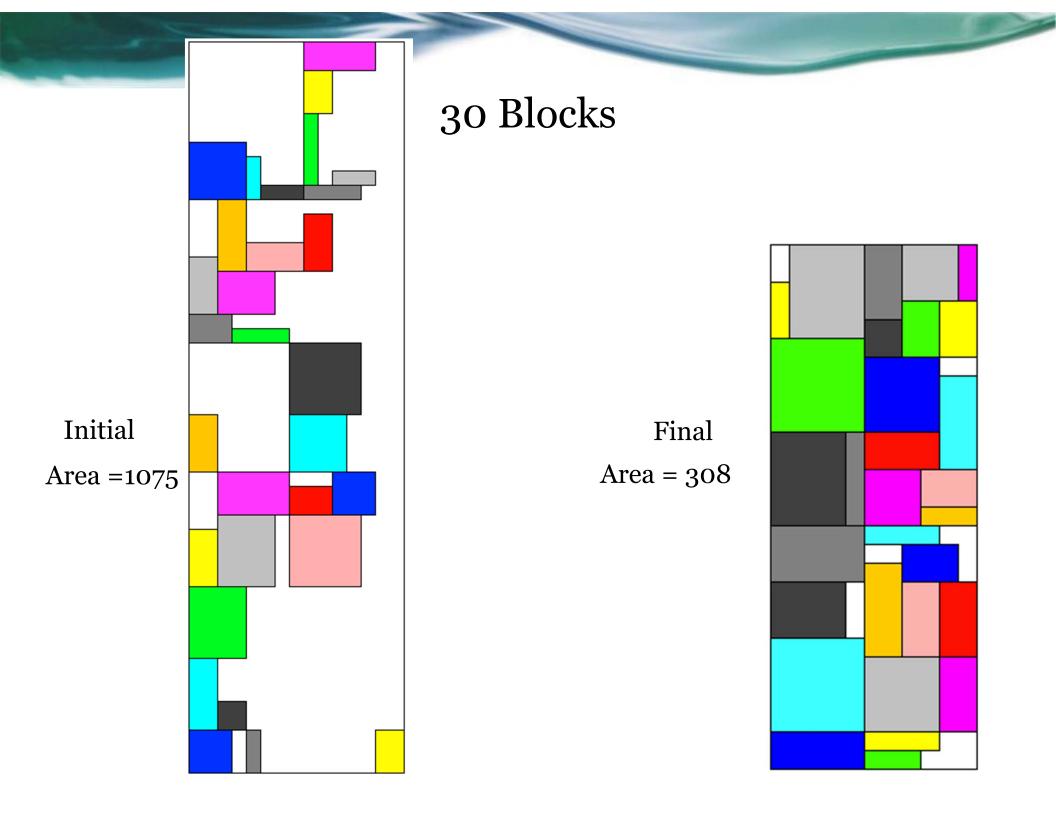

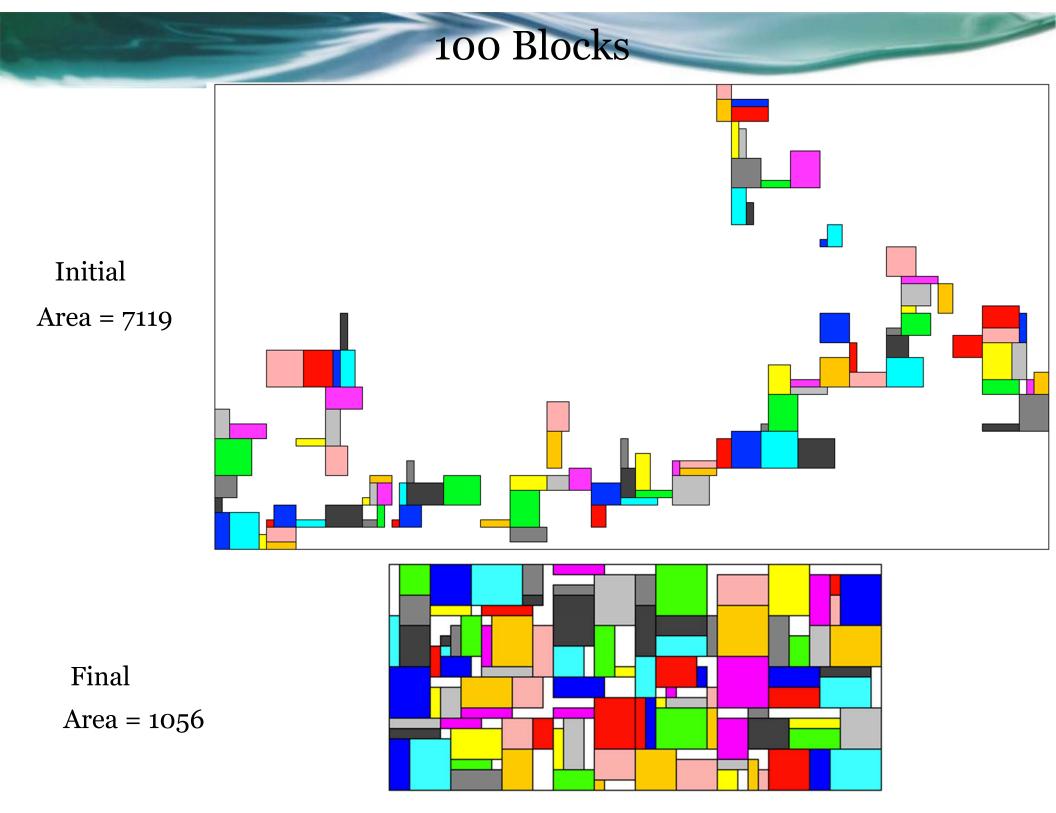

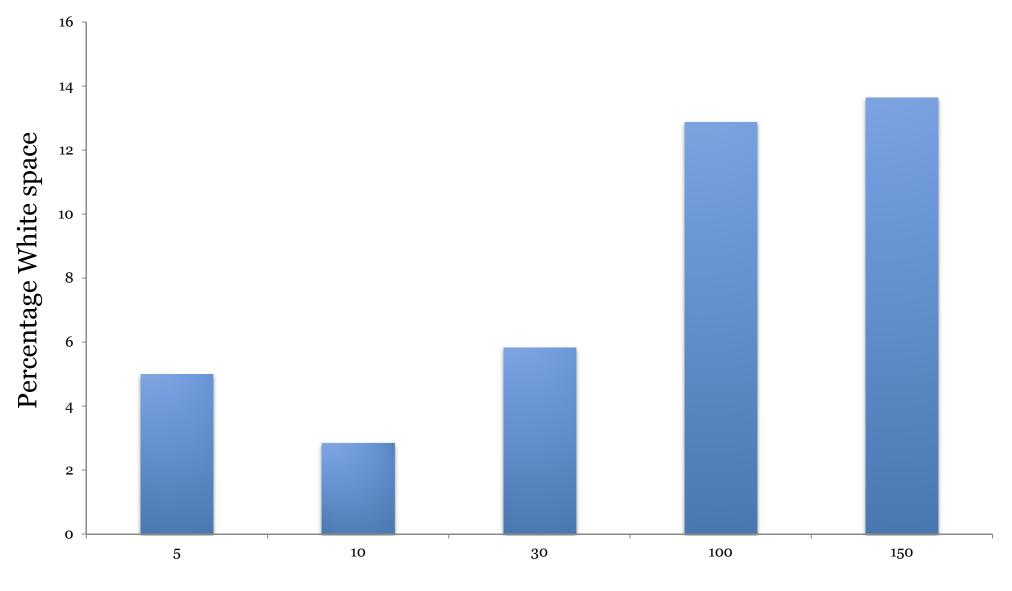

### **Experimental Results**

| No. of<br>Block | Initial Area | Final Area | Percentage<br>Improvement | Time in Min |

|-----------------|--------------|------------|---------------------------|-------------|

| 5               | 68           | 40         | 41.17647059               | 0.00006625  |

| 10              | 147          | 70         | 52.38095238               | 0.002007383 |

| 30              | 1075         | 308        | 71.34883721               | 0.017282667 |

| 100             | 7119         | 1056       | 85.16645596               | 0.527993333 |

| 150             | 14104        | 1554       | 88.98184912               | 8.006683333 |

No of Blocks

### Challenges

- Finding the initial parameters for simulated annealing which give minimum floorplan area.

- Reducing the run time and the memory requirement for simulated annealing.

### Future Scope

- Use wire length as additional parameter in the cost function for simulated annealing.

- Add support for soft and L shaped blocks.

### Conclusion

- Simulated annealing can reduce the floorplan area significantly but for the large circuits with higher initial temperature it has a long runtime.

- Runtime depends on the no of blocks, initial temperature, cooling ratio, no of moves per temperature and freezing temperature.

- No of rejected moves are more at higher temperatures.

- For our implementation there was good reduction in the floorplan area with low runtime.

# Questions ?

## Thank You

### Reference

- Sung Kyu Lim, "Practical Problems in VLSI Physical Design Automation," Springer, July 2008

- D. F. Wong and C. L. Liu, "Floorplan design of VLSI circuits", Algorithmica, 4(1), pp 263-291, 1989.