SWITCH DESIGN CHAPTER II-1 SWITCH DESIGN •CHAPTER II

# **CHAPTER II**

# SWITCH NETWORKS AND SWITCH DESIGN

# Analog vs Digital

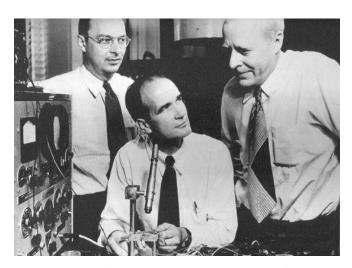

# Transistor: Electrical Switch

Bardee, Shockley, Brattain (Bell Labs, 1948), Nobel Prize Winners

bipolar transistor (single TR)

field-effect transistor (many TR)

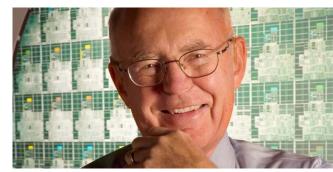

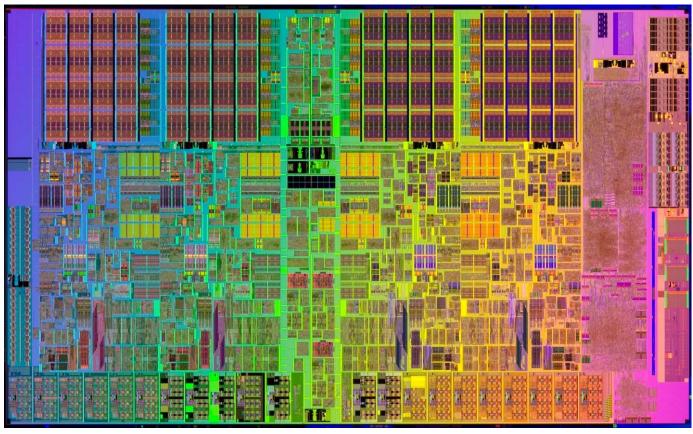

# Modern Integrated Circuits

- How many transistors do you see?

- How small are they?

#### SWITCH DESIGN CHAPTER II-2 SWITCH DESIGN

#### **SWITCH NETWORKS**

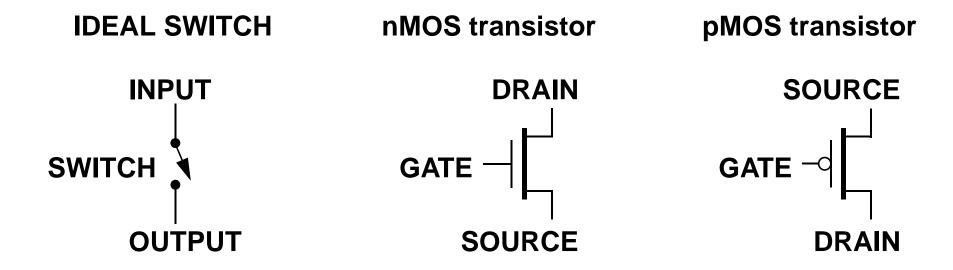

**BASIC IDEAL SWITCH**

**•SWITCH NETWORKS**

Simplest structure in a computing system is a switch

#### **IDEAL SWITCH**

- Path exists between INPUT and OUTPUT if Switch is CLOSED or ON

- Path does not exist between INPUT and OUTPUT if SWITCH is OPEN or OFF

#### SWITCH DESIGN CHAPTER II-6 SWITCH DESIGN

# **CMOS**CMOS SWITCHES

•SWITCH NETWORKS

- -SWITCHES IN SERIES

- -SWITCHES IN PARALLEL

- -INPUT SELECTOR

- The idea is to use the series and parallel switch configurations to route signals in a desired fashion.

- Unfortunately, it is difficult to implement an ideal switch as given.

- Complementary Metal Oxide Semiconductor (CMOS) devices give us some interesting components.

SWITCH DESIGN CHAPTER II-7 SWITCH DESIGN

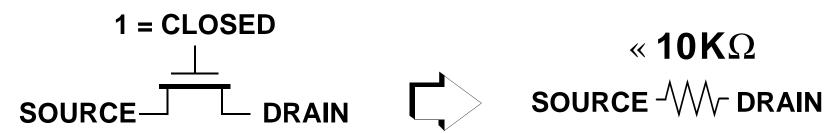

# **CMOS**TRANSFER CHARACTERISTICS

•SWITCH NETWORKS

•CMOS

-CMOS SWITCHES

| nMOS           | _           |        |

|----------------|-------------|--------|

| s <sup>-</sup> | <b>- </b> [ | _<br>_ |

| S | SWITCH |  |  |

|---|--------|--|--|

| 0 | OPEN   |  |  |

| 1 | CLOSED |  |  |

- nMOS when CLOSED

- Transmits logic level 0 well

- Transmits logic level 1 poorly

| S | SWITCH |  |  |

|---|--------|--|--|

| 0 | CLOSED |  |  |

| 1 | OPEN   |  |  |

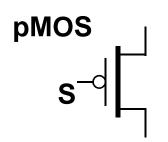

- pMOS when CLOSED

- Transmits logic level 1 well

- Transmits logic level 0 poorly

**SWITCH DESIGN CHAPTER II-8 SWITCH DESIGN**

# **CMOS**

TRANSMISSION GATE (1)

- **•SWITCH NETWORKS**

- •CMOS

- -CMOS SWITCHES

- -TRANSFER CHAR.

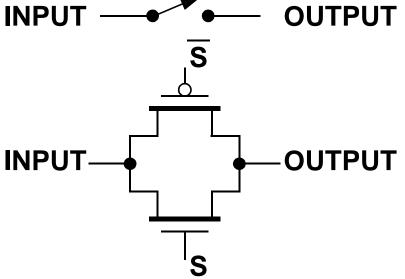

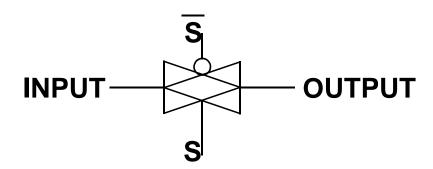

**IDEAL SWITCH**

**CMOS TRANSMISSION GATE** (SWITCH)

| S | nMOS | pMOS | OUTPUT |

|---|------|------|--------|

| 0 | OFF  | OFF  | Z      |

| 1 | ON   | ON   | INPUT  |

SWITCH DESIGN CHAPTER II-9 SWITCH DESIGN

#### **CMOS**

TRANSMISSION GATE (2)

- •CMOS

- -CMOS SWITCHES

- -TRANSFER CHAR.

- -TRANSMISSION GATE

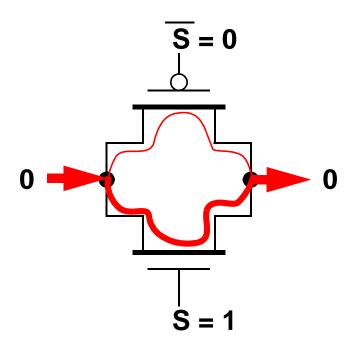

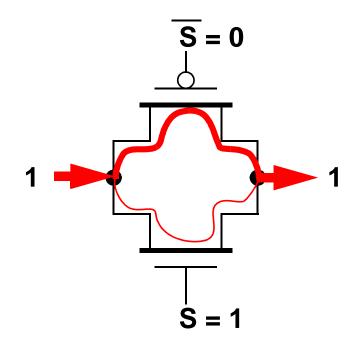

# SPLIT OF CURRENT ACROSS A TRANSMISSION GATE FOR LOGIC-0 AND LOGIC-1 INPUT

#### **LOGIC-0 AT INPUT**

#### **LOGIC-1 AT INPUT**

#### SWITCH DESIGN CHAPTER II-10 SWITCH DESIGN

## **SWITCH NETWORKS**

#### HIGH IMPEDANCE $\mathbf{Z}$ (1)

•CMOS

- -CMOS SWITCHES

- -TRANSFER CHAR.

- -TRANSMISSION GATE

- With switches, we can consider three states for an output:

- Logic-0

- Logic-1

- High Impedance Z

- Path exists for Logic-0 and Logic-1 when the switch is CLOSED.

High impedance is a state where the switch is OPEN.

#### SWITCH DESIGN CHAPTER II-11 SWITCH DESIGN

#### **SWITCH NETWORKS**

HIGH IMPEDANCE  $\mathbf{Z}$  (2)

•CMOS•SWITCH NETWORKS-HIGH IMPEDANCE Z

- Another way of thinking of switches is as follows

- Path exists for Logic-0 and Logic-1 when the switch is CLOSED, meaning that the impedance/resistance is small enough to allow amply flow of current.

High impedance is a state where the switch is OPEN, meaning that the impedance/resistance is very large allowing nearly no current flow.

SWITCH DESIGN CHAPTER II-12 SWITCH DESIGN

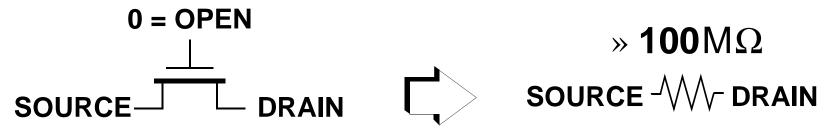

# **SWITCH NETWORKS**

INVERTER (NOT)

•CMOS

•SWITCH NETWORKS

-HIGH IMPEDANCE Z

This network inverts the binary input value.

SWITCH DESIGN CHAPTER II-13 SWITCH DESIGN

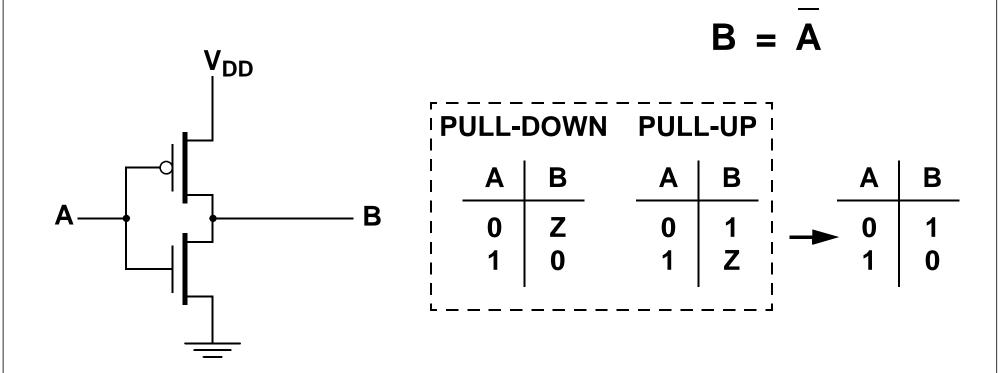

# **SWITCH NETWORKS**

NAND NETWORK

- •CMOS

- •SWITCH NETWORKS

- -HIGH IMPEDANCE Z

- -INVERTER

$$C = \overline{AB}$$

| [    | PULL-DOWN |   |   | PULL-UP |   | <br> |   |             |   |   |   |

|------|-----------|---|---|---------|---|------|---|-------------|---|---|---|

| <br> | _         | Α | В | С       | Α | В    | С | i<br>I .    | Α | В | С |

| [    |           | 0 | 0 | Z       | 0 | 0    | 1 | I<br>I      | 0 | 0 | 1 |

| <br> |           | 0 | 1 | Z       | 0 | 1    | 1 | <del></del> | 0 | 1 | 1 |

| <br> |           | 1 | 0 | Z       | 1 | 0    | 1 | I<br>I      | 1 | 0 | 1 |

| I    |           | 1 | 1 | 0       | 1 | 1    | Z | <br>        | 1 | 1 | 0 |

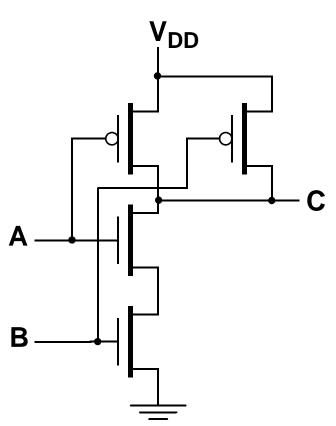

**SWITCH DESIGN CHAPTER II-14 SWITCH DESIGN**

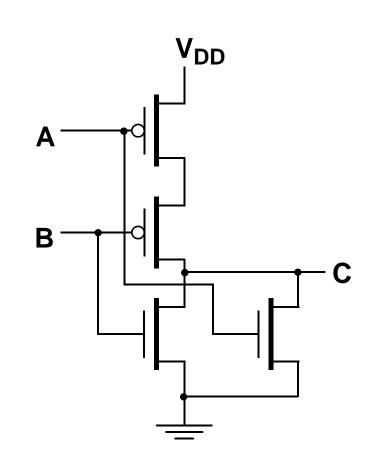

## **SWITCH NETWORKS**

NOR NETWORK

В

- **•SWITCH NETWORKS**

- -HIGH IMPEDANCE Z

- -INVERTER

- -NAND NETWORK

$C = \overline{A + B}$

SWITCH DESIGN CHAPTER II-15 SWITCH DESIGN

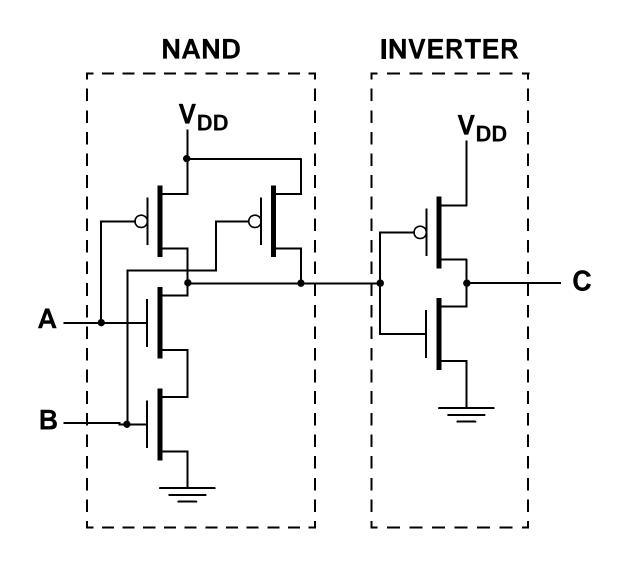

# **SWITCH NETWORKS**

AND NETWORK

- **•SWITCH NETWORKS**

- -INVERTER

- -NAND NETWORK

- -NOR NETWORK

$$C = AB$$

SWITCH DESIGN CHAPTER II-16 SWITCH DESIGN

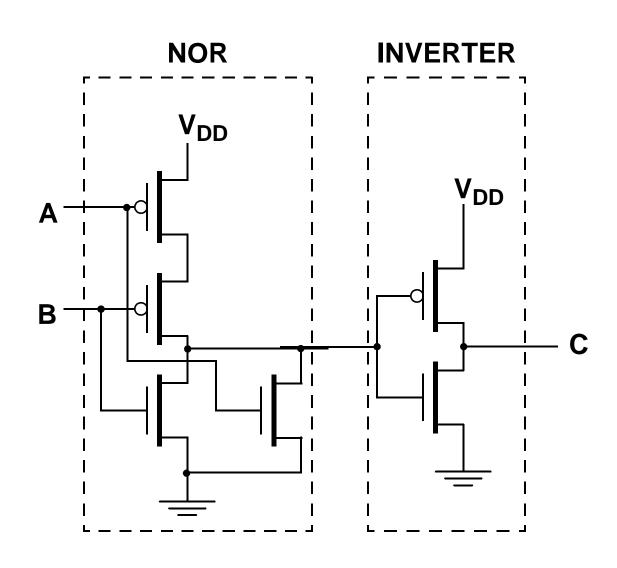

# **SWITCH NETWORKS**

OR NETWORK

- **•SWITCH NETWORKS**

- -NAND NETWORK

- -NOR NETWORK

- -AND NETWORK

$$C = A + B$$

| Α | В | С |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

SWITCH DESIGN CHAPTER II-17 SWITCH DESIGN

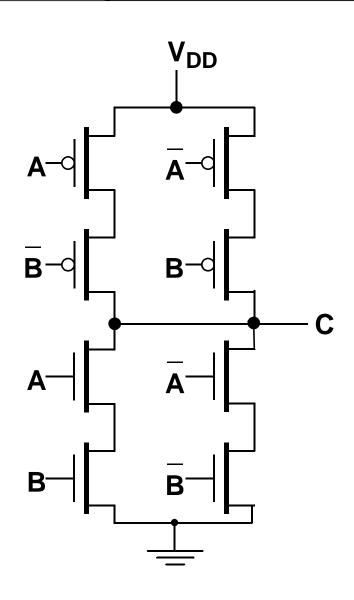

# **SWITCH NETWORKS**

XOR NETWORK

- **•SWITCH NETWORKS**

- -NOR NETWORK

- -AND NETWORK

- **-OR NETWORK**

$$C = AB + AB$$

| A | В | C |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

|   |   | I |

SWITCH DESIGN CHAPTER II-18 SWITCH DESIGN

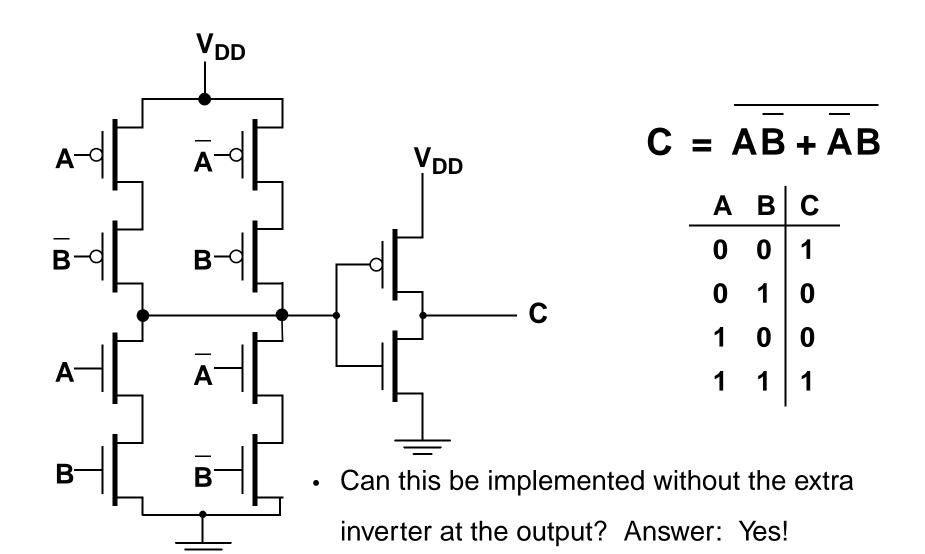

## **SWITCH NETWORKS**

**XNOR NETWORK**

- **•SWITCH NETWORKS**

- -AND NETWORK

- **-OR NETWORK**

- -XOR NETWORK

SWITCH DESIGN CHAPTER II-19 SWITCH DESIGN

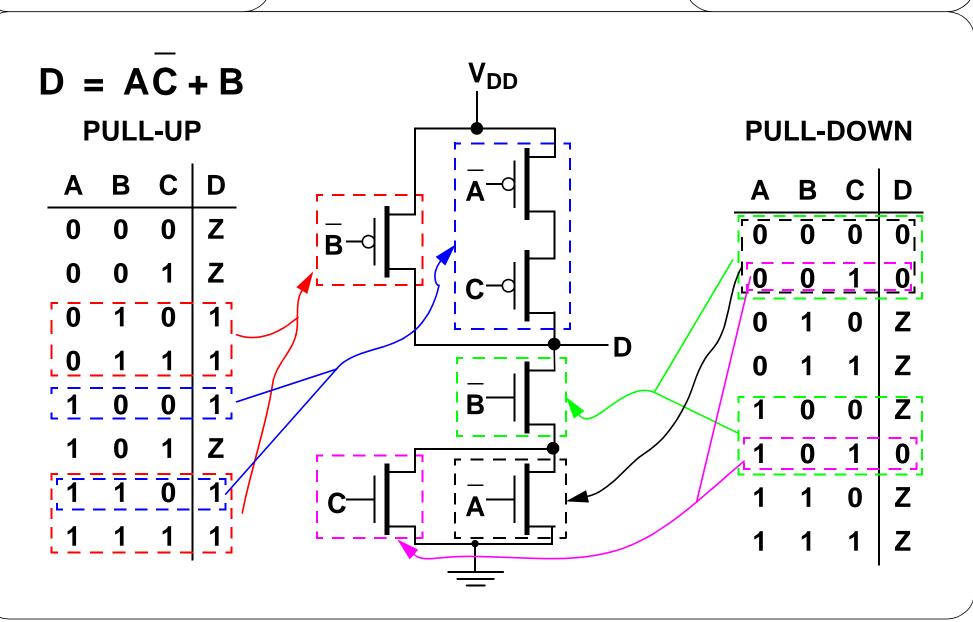

## **SWITCH NETWORKS**

PULL-UP/PULL-DOWN

- **•SWITCH NETWORKS**

- -OR NETWORK

- -XOR NETWORK

- -XNOR NETWORK

#### SWITCH DESIGN CHAPTER II-20 SWITCH DESIGN

# **SWITCH NETWORKS**

#### **FUNCTION IMPLEMENTATION**

SWITCH NETWORKS

- -XOR NETWORK

- -XNOR NETWORK

- -PULL-UP/PULL-DOWN

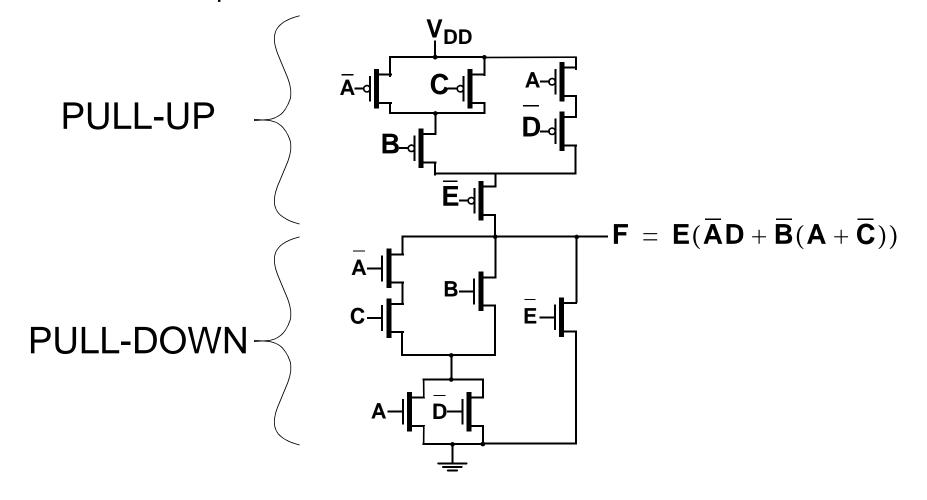

- Most Boolean functions can be easily implemented using switches.

- The basic rules are as follows

- Pull-up section of switch network

- Use complements for all literals in expression

- Use only pMOS devices

- Form series network for an AND operation

- Form parallel network for an OR operation

- Pull-down section of switch network

- Use complements for all literals in expression

- Use only nMOS devices

- Form parallel network for an AND operation

- Form series network for an OR operation

#### SWITCH DESIGN CHAPTER II-21 SWITCH DESIGN

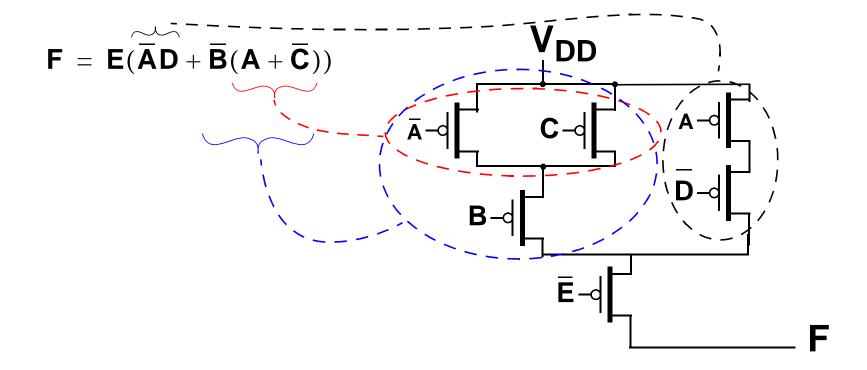

#### **SWITCH NETWORKS**

**EXAMPLE PULL-UP**

- •SWITCH NETWORKS

- -XNOR NETWORK

- -PULL-UP/PULL-DOWN

- -FUNC. IMPLEMENTATION

- To implement the Boolean function given below, the following pull-up network could be designed.

#### SWITCH DESIGN CHAPTER II-22 SWITCH DESIGN

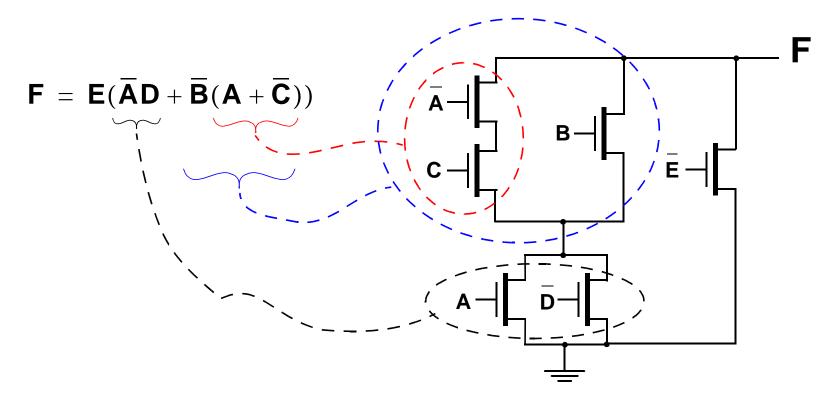

#### **SWITCH NETWORKS**

**EXAMPLE PULL-DOWN**

- •SWITCH NETWORKS

-PULL-UP/PULL-DOWN

- -FUNC. IMPLEMENTATION

- -EXAMPLE PULL-UP

- To complete the switch design, the pull-down section for the Boolean function must also be designed.

Notice how AND and OR become OR and AND circuits, respectively.

#### SWITCH DESIGN CHAPTER II-23 SWITCH DESIGN

#### **SWITCH NETWORKS**

COMPLETED EXAMPLE

- **•SWITCH NETWORKS**

- -FUNC. IMPLEMENTATION

- -EXAMPLE PULL-UP

- -EXAMPLE PULL-DOWN

- Putting the pull-up and pull-down pieces together gives the following

CMOS switch implementation of the Boolean function.